| ÐлекÑÑоннÑй компоненÑ: LTC1345 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

1

LTC1345

Single Supply

V.35 Transceiver

s

Single Chip Provides All V.35 Differential Clock

and Data Signals

s

Operates From Single 5V Supply

s

Software Selectable DTE or DCE Configuration

s

Transmitters and Receivers Will Withstand

Repeated

±

10kV ESD Pulses

s

Shutdown Mode Reduces I

CC

to 1

µ

A Typ

s

10MBaud Transmission Rate

s

Transmitter Maintains High Impedance When

Disabled, Shut Down, or with Power Off

s

Meets CCITT V.35 Specification

s

Transmitters are Short-Circuit Protected

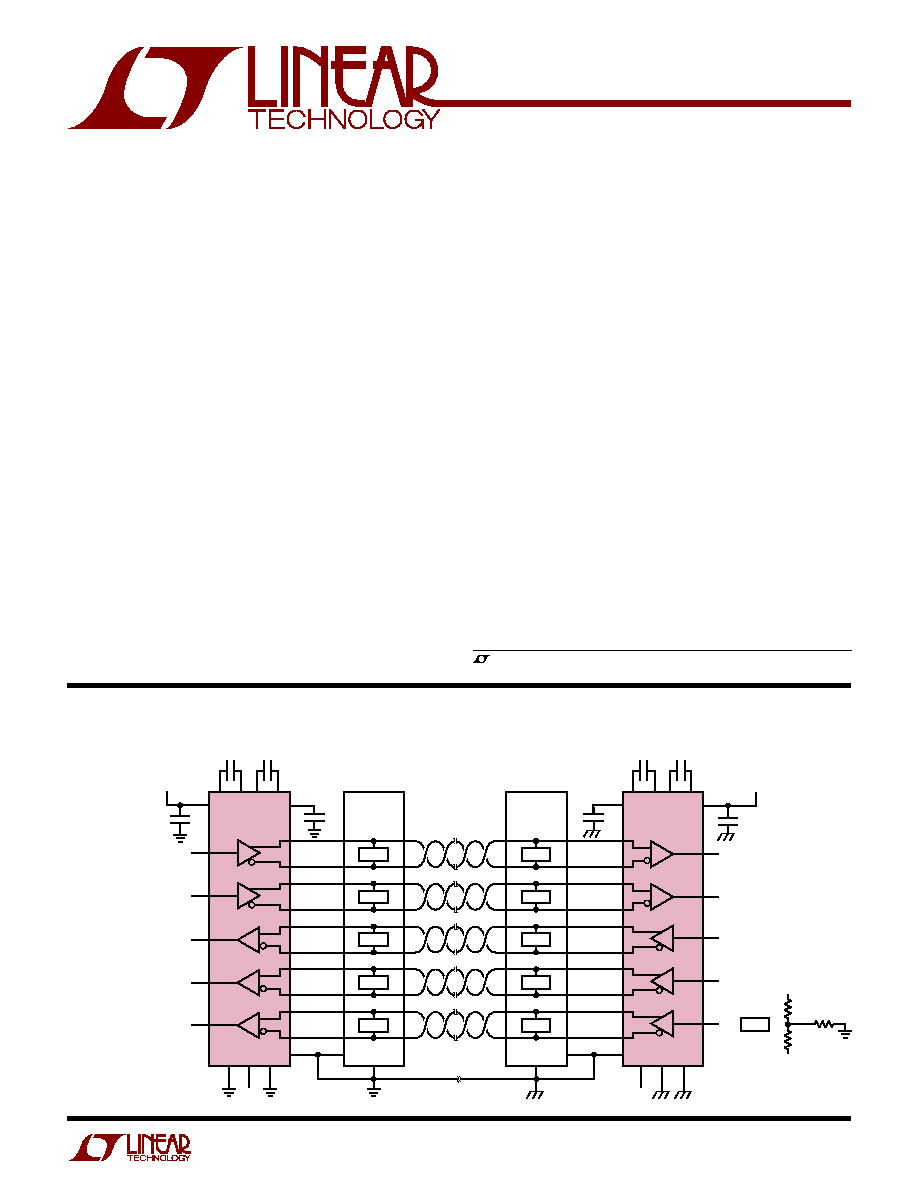

The LTC

®

1345 is a single chip transceiver that provides the

differential clock and data signals for a V.35 interface from

a single 5V supply. Combined with an external resistor

termination network and an LT

®

1134A RS232 transceiver

for the control signals, the LTC1345 forms a complete low

power DTE or DCE V.35 interface port operating from a

single 5V supply.

The LTC1345 features three current output differential

transmitters, three differential receivers, and a charge

pump. The transceiver can be configured for DTE or DCE

operation or shut down using two Select pins. In the

Shutdown mode, the supply current is reduced to 1

µ

A.

The transceiver operates up to 10Mbaud. All transmitters

feature short-circuit protection and a Receiver Output

Enable pin allows the receiver outputs to be forced into a

high impedance state. Both transmitter outputs and re-

ceiver inputs feature

±

10kV ESD protection. The charge

pump features a regulated V

EE

output using three external

1

µ

F capacitors.

s

Modems

s

Telecommunications

s

Data Routers

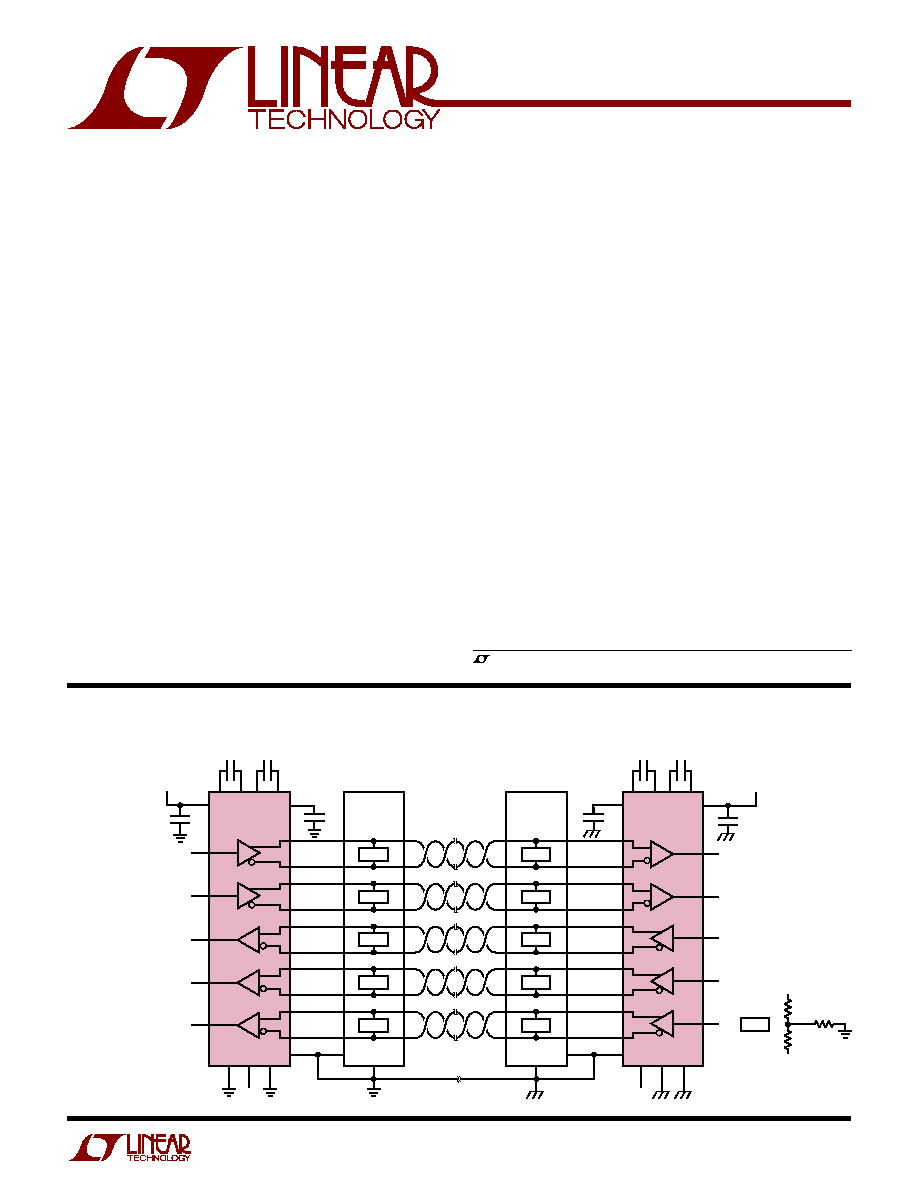

Clock and Data Signals for V.35 Interface

DCE

DTE

, LTC and LT are registered trademarks of Linear Technology Corporation.

4

1

µ

F

V

CC1

5V

2

1

1

µ

F

1

µ

F

1

µ

F

1

µ

F

28

27

3

6

1

2

26

25

12

12

11

18

17

1

µ

F

DX

LTC1345

LTC1345

BI

627T500/1250

BI

627T500/1250

BI TECHNOLOGIES

627T500/1250 (SOIC) OR

899TR50/125 (DIP)

28

V

CC2

5V

1

2

1

µ

F

4

3

27

1

µ

F

RX

T

TXD (103)

SCTE (113)

TXC (114)

RXC (115)

RXD (104)

GND (102)

T

7

3

4

24

23

10

13

9

16

15

DX

RX

T

T

11

14

13

20

19

1

6

2

26

25

T

T

12

12

11

18

17

10

14

8

9

3

7

4

24

23

T

T

8

13

10

9

16

15

7

5

5

7

5

8

6

22

21

T

T

RX

RX

RX

V

CC1

10

14

LTC1345 · TA01

9

V

CC2

DX

DX

DX

50

=

125

T

50

FEATURES

DESCRIPTIO

U

APPLICATIO S

U

TYPICAL APPLICATIO

U

2

LTC1345

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

OD

Transmitter Differential Output Voltage

Figure 1, 4V

V

OS

4V

q

0.44

0.55

0.66

V

V

OC

Transmitter Common-Mode Output Voltage

Figure 1, V

OS

= 0V

q

0.6

0

0.6

V

I

OH

Transmitter Output High Current

V

Y, Z

= 0V

q

12.6

11

9.4

mA

I

OL

Transmitter Output Low Current

V

Y, Z

= 0V

q

9.4

11

12.6

mA

I

OZ

Transmitter Output Leakage Current

S1 = S2 = 0V, 5V

V

Y, Z

5V

q

±

1

±

100

µ

A

R

O

Transmitter Output Impedance

2V

V

Y, Z

2V

100

k

V

TH

Differential Receiver Input Threshold Voltage

7V

(V

A

+ V

B

)/2

7V

q

25

200

mV

V

TH

Receiver Input Hysterisis

7V

(V

A

+ V

B

)/2

7V

50

mV

I

IN

Receiver Input Current (A, B)

7V

V

A, B

7V

q

0.4

mA

R

IN

Receiver Input Impedance

7V

V

A, B

7V

q

17.5

30

k

V

OH

Receiver Output High Voltage

I

O

= 4mA, V

B, A

= 0.2V

q

3

4.5

V

V

OL

Receiver Output Low Voltage

I

O

= 4mA, V

B, A

= 0.2V

q

0.2

0.4

V

I

OSR

Receiver Output Short-Circuit Current

0V

V

O

V

CC

q

7

85

mA

I

OZR

Receiver Three-State Output Current

S1 = S2 = 0V, 0V

V

O

V

CC

q

±

10

µ

A

V

IH

Logic Input High Voltage

T, S1, S2, OE

q

2

V

V

IL

Logic Input Low Voltage

T, S1, S2, OE

q

0.8

V

I

IN

Logic Input Current

T, S1, S2, OE

q

±

10

µ

A

I

CC

V

CC

Supply Current

Figure 1, V

OS

= 0, S1 = S2 = HIGH

q

118

170

mA

No Load, S1 = S2 = HIGH

q

19

30

mA

Shutdown, S1 = S2 = 0V

q

1

100

µ

A

V

EE

V

EE

Voltage

No Load, S1 = S2 = HIGH

5.5

V

ORDER PART

NUMBER

THREE V.35 TRANSMITTERS AND THREE RECEIVERS

T

JMAX

= 125

°

C,

JA

= 56

°

C/W (NW)

T

JMAX

= 125

°

C,

JA

= 65

°

C/W (SW)

Consult factory for Military grade parts.

The

q

denotes specifications which apply over the full operating

temperature range, otherwise specifications are at T

A

= 25

°

C. V

CC

= 5V

±

5% (Notes 2, 3), unless otherwise specified.

(Note 1)

Supply Voltage, V

CC

.................................................. 6V

Input Voltage

Transmitters ........................... 0.3V to (V

CC

+ 0.3V)

Receivers ............................................... 18V to 18V

S1, S2, OE ............................... 0.3V to (V

CC

+ 0.3V)

Output Voltage

Transmitters .......................................... 18V to 18V

Receivers ................................ 0.3V to (V

CC

+ 0.3V)

V

EE

........................................................ 10V to 0.3V

Short-Circuit Duration

Transmitter Output ..................................... Indefinite

Receiver Output .......................................... Indefinite

V

EE

................................................................. 30 sec

Operating Temperature Range

Commercial ............................................ 0

°

C to 70

°

C

Industrial ........................................... 40

°

C to 85

°

C

Storage Temperature Range ................ 65

°

C to 150

°

C

Lead Temperature (Soldering, 10 sec)................. 300

°

C

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

C2

+

C1

+

V

CC

C1

GND

T1

T2

T3

S1

S2

R3

R2

R1

OE

C2

V

EE

Y1

Z1

Y2

Z2

Y3

Z3

B3

A3

B2

A2

B1

A1

NW PACKAGE

28-LEAD PDIP

SW PACKAGE

28-LEAD PLASTIC SO

TOP VIEW

LTC1345CNW

LTC1345CSW

LTC1345INW

LTC1345ISW

ABSOLUTE AXI U RATI GS

W

W

W

U

PACKAGE/ORDER I FOR ATIO

U

U

W

DC ELECTRICAL CHARACTERISTICS

3

LTC1345

Note 1: The absolute maximum ratings are those values beyond which the

safety of the device cannot be guaranteed.

Note 2: All currents into device pins are termed positive; all currents out of

device pins are termed negative. All voltages are referenced to device

ground unless otherwise specified.

Note 3: All typicals are given for V

CC

= 5V, C1 = C2 = C3 = 1

µ

F ceramic

capacitors and T

A

= 25

°

C.

Note 4: Maximum data rate is specified for NRZ data encoding scheme.

The maximum data rate may be different for other data encoding schemes.

Data rate is guaranteed by correlation and is not tested.

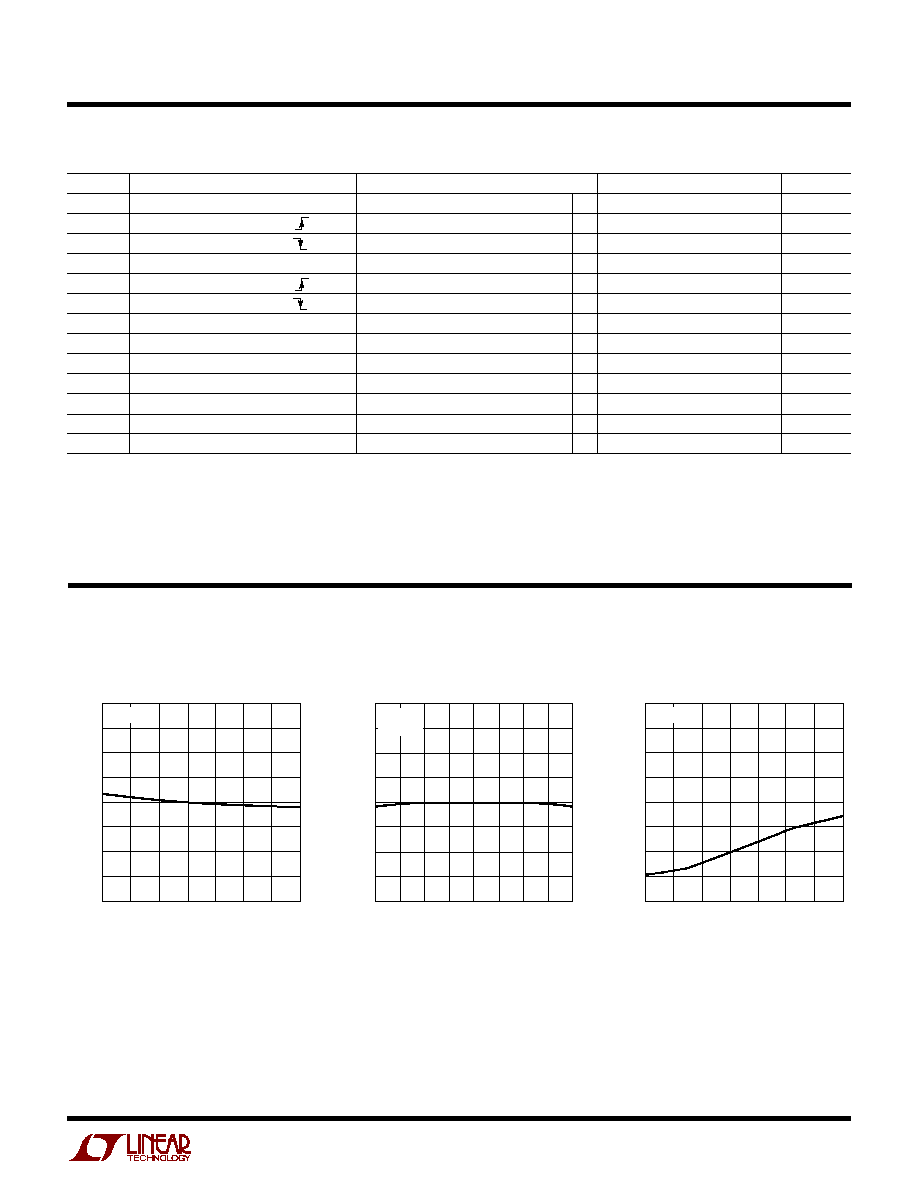

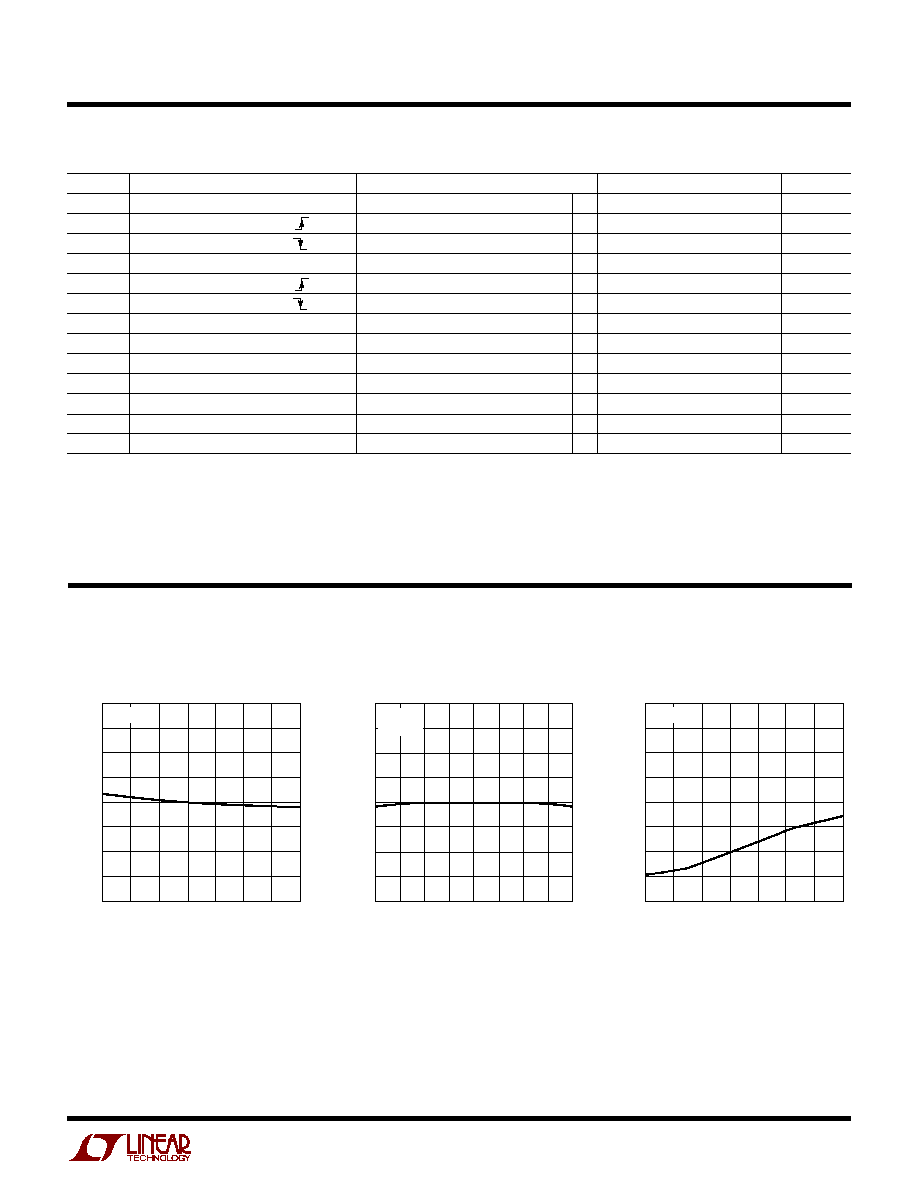

TEMPERATURE (°C)

50

OUTPUT CURRENT

(mA)

25

LTC1345 · TPC01

11

10

25

0

50

9

13

12

75

100

125

V

CC

= 5V

Transmitter Output Current

vs Temperature

TEMPERATURE (°C)

50

TIME (ns)

25

LTC1345 · TPC03

10

5

25

0

50

0

20

15

75

100

125

V

CC

= 5V

Transmitter Output Skew

vs Temperature

OUTPUT VOLTAGE (V)

2.0

OUTPUT CURRENT

(mA)

11

12

2.0

LTC1345 · TPC02

10

9

1.0

0

1.0

13

1.5

0.5

0.5

1.5

T

A

= 25

°

C

V

CC

= 5V

Transmitter Output Current

vs Output Voltage

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

t

R

, t

F

Transmitter Rise or Fall Time

Figures 1 and 3, V

OS

= 0V

q

7

40

ns

t

PLH

Transmitter Input to Output

Figures 1 and 3, V

OS

= 0V

q

25

70

ns

t

PHL

Transmitter Input to Output

Figures 1 and 3, V

OS

= 0V

q

25

70

ns

t

SKEW

Transmitter Output to Output

Figures 1 and 3, V

OS

= 0V

0

ns

t

PLH

Receiver Input to Output

Figures 1 and 4, V

OS

= 0V

q

49

100

ns

t

PHL

Receiver Input to Output

Figures 1 and 4, V

OS

= 0V

q

52

100

ns

t

SKEW

Differential Receiver Skew, t

PLH

t

PHL

Figures 1 and 4, V

OS

= 0V

3

ns

t

ZL

Receiver Enable to Output LOW

Figures 2 and 5, C

L

= 15pF, S1 Closed

q

40

70

ns

t

ZH

Receiver Enable to Output HIGH

Figures 2 and 5, C

L

= 15pF, S2 Closed

q

35

70

ns

t

LZ

Receiver Disable From LOW

Figures 2 and 5, C

L

= 15pF, S1 Closed

q

30

70

ns

t

HZ

Receiver Disable From HIGH

Figures 2 and 5, C

L

= 15pF, S2 Closed

q

35

70

ns

f

OSC

Charge Pump Oscillator Frequency

200

kHz

BR

MAX

Maximum Data Rate (Note 4)

q

10

15

Mbaud

AC ELECTRICAL CHARACTERISTICS

The

q

denotes specifications which apply over the full operating

temperature range, otherwise specifications are at T

A

= 25

°

C. V

CC

= 5V

±

5% (Notes 2, 3), unless otherwise specified.

TYPICAL PERFOR A CE CHARACTERISTICS

U

W

4

LTC1345

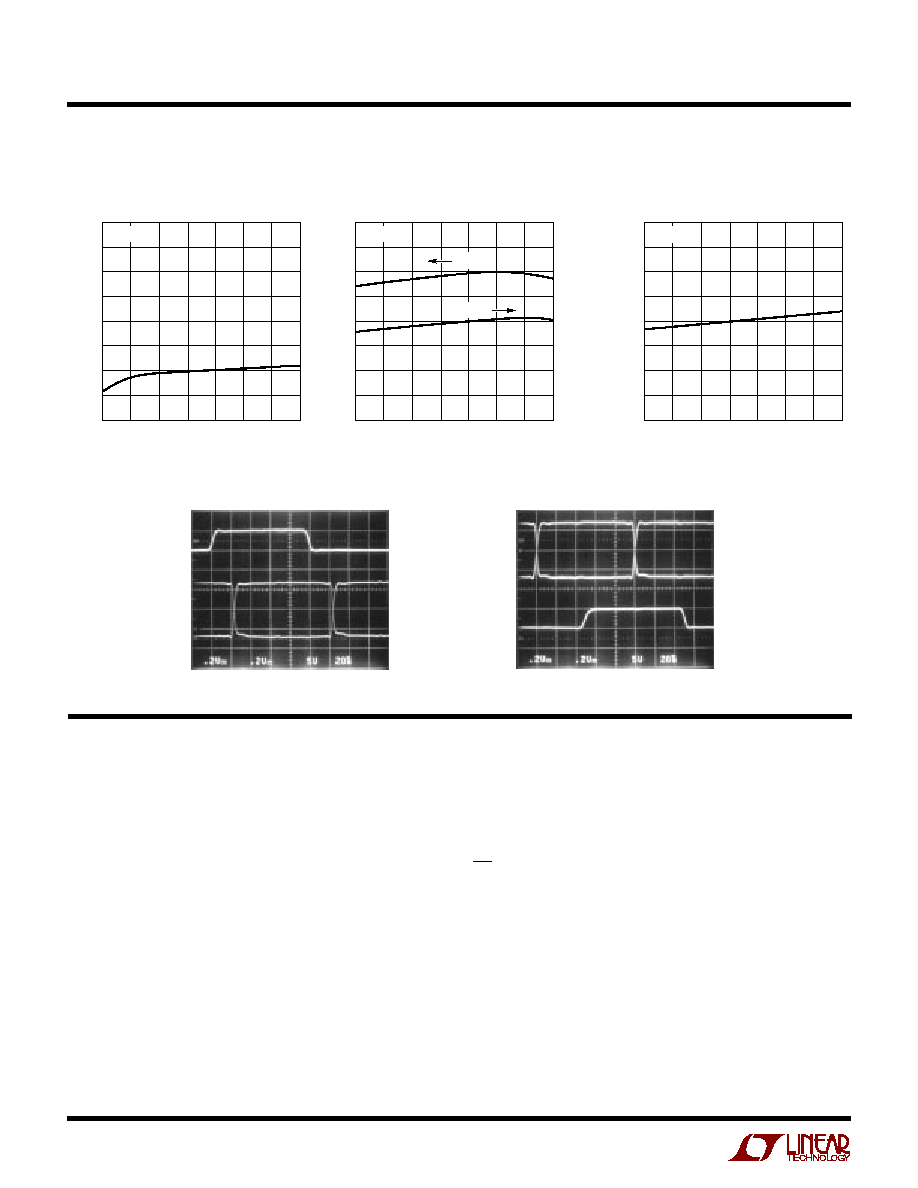

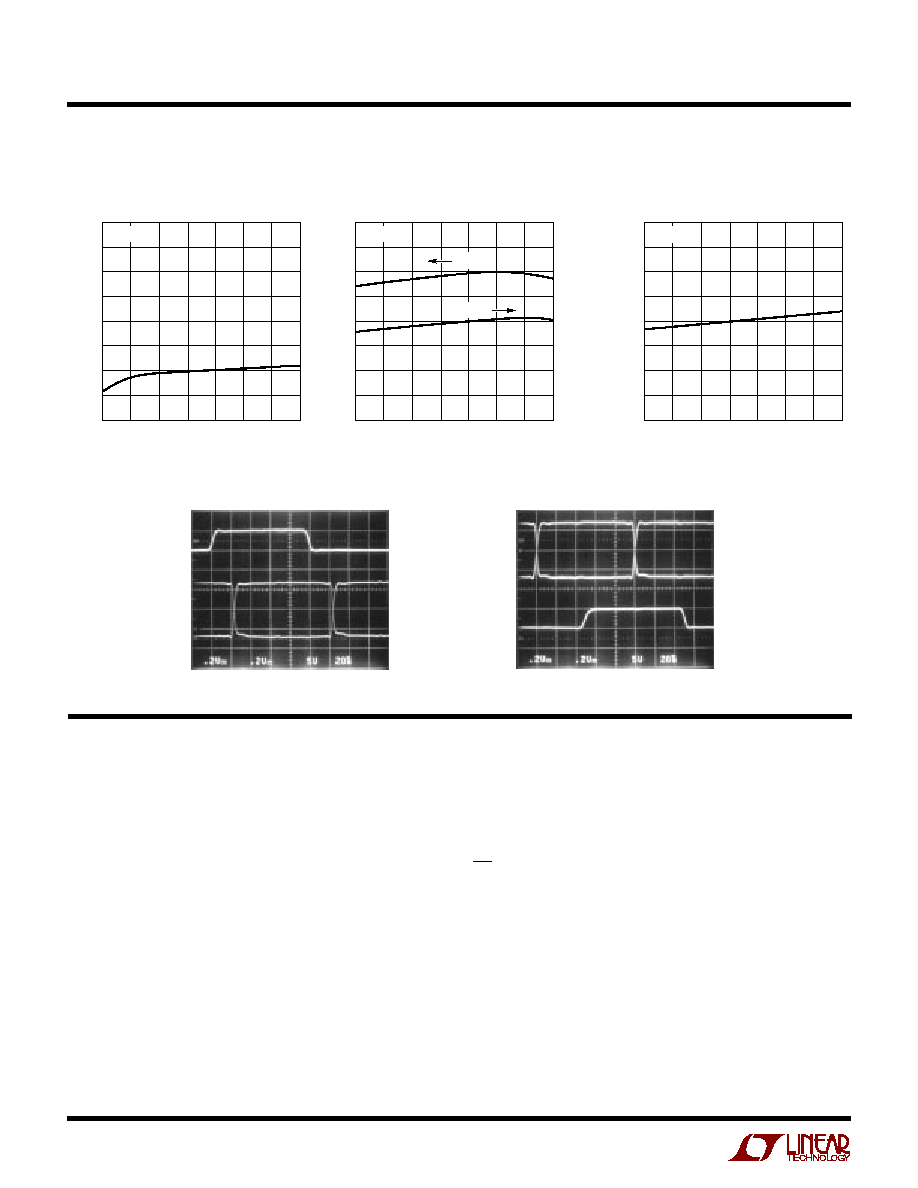

Receiver

t

PLH

t

PHL

vs Temperature

TEMPERATURE (°C)

50

TIME (ns)

25

LTC1345 · TPC04

10

5

25

0

50

0

20

15

75

100

125

V

CC

= 5V

V

EE

Voltage vs Temperature

TEMPERATURE (°C)

50

VOLTAGE (V)

25

LTC1345 · TPC06

5.5

6.0

25

0

50

6.5

4.5

5.0

75

100

125

V

CC

= 5V

Supply Current vs Temperature

TEMPERATURE (°C)

50

CURRENT (mA)

CURRENT (mA)

25

LTC1345 · TPC05

100

80

25

0

50

60

140

120

20

15

10

30

25

75

100

125

V

CC

= 5V

LOADED

NO LOAD

Receiver Output Waveforms

R3 (Pin 11): Receiver 3 Output.

R2 (Pin 12): Receiver 2 Output.

R1 (Pin 13): Receiver 1 Output.

OE (Pin 14): Receiver Output Enable.

A1 (Pin 15): Receiver 1 Inverting Input.

B1 (Pin 16): Receiver 1 Noninverting Input.

A2 (Pin 17): Receiver 2 Inverting Input.

B2 (Pin 18): Receiver 2 Noninverting Input.

A3 (Pin 19): Receiver 3 Inverting Input.

B3 (Pin 20): Receiver 3 Noninverting Input.

Z3 (Pin 21): Transmitter 3 Inverting Output.

C2

+

(Pin 1): Capacitor C2 Positive Terminal.

C1

+

(Pin 2): Capacitor C1 Positive Terminal.

V

CC

(Pin 3): Positive Supply, 4.75

V

CC

5.25V.

C1

(Pin 4): Capacitor C1 Negative Terminal.

GND (Pin 5): Ground. The positive terminal of C3 is

connected to ground.

T1 (Pin 6): Transmitter 1 Input.

T2 (Pin 7): Transmitter 2 Input.

T3 (Pin 8): Transmitter 3 Input.

S1 (Pin 9): Select Input 1.

S2 (Pin 10): Select Input 2.

Transmitter Output Waveforms

INPUT

5V/DIV

OUTPUT

5V/DIV

OUTPUT

0.2V/DIV

LTC1345 · TPC07

INPUT

0.2/DIV

LTC1345 · TPC08

TYPICAL PERFOR A CE CHARACTERISTICS

U

W

U

U

U

PI FU CTIO S

5

LTC1345

Y3 (Pin 22): Transmitter 3 Noninverting Output.

Z2 (Pin 23): Transmitter 2 Inverting Output.

Y2 (Pin 24): Transmitter 2 Noninverting Output

Z1 (Pin 25): Transmitter 1 Inverting Output.

Y1 (Pin 26): Transmitter 1 Noninverting Output.

V

EE

(Pin 27): Charge Pump Output. Connected to negative

terminal of capacitor C3.

C2

(Pin 28): Capacitor C2 Negative Terminal.

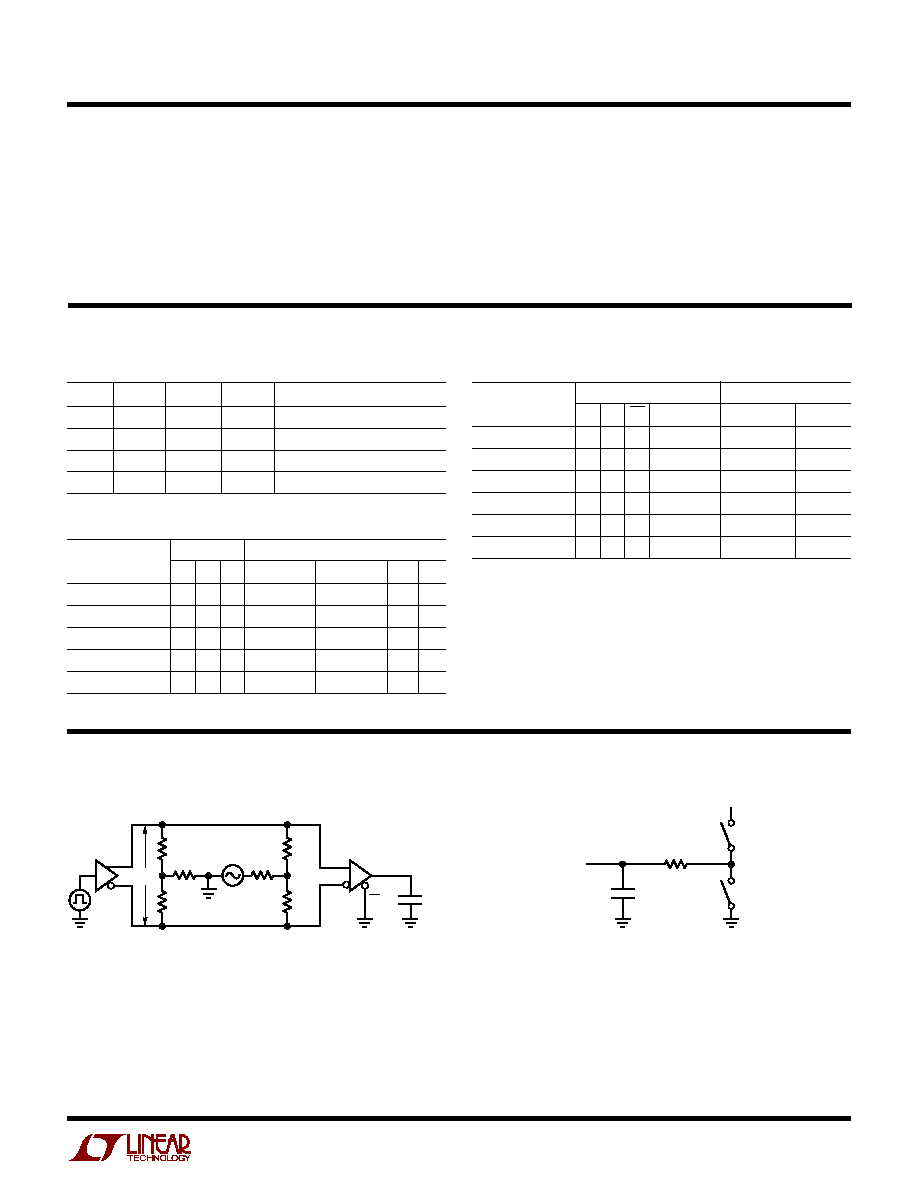

Transmitter and Receiver Configuration

S1

S2

TX#

RX#

REMARKS

0

0

--

--

Shutdown

1

0

1, 2, 3

1, 2

DCE Mode, RX3 Shut Down

0

1

1, 2

1, 2, 3

DTE Mode, TX3 Shut Down

1

1

1, 2, 3

1, 2, 3

All Active

Transmitter

INPUTS

OUTPUTS

CONFIGURATION

S1 S2

T

Y1 AND Y2

Z1 AND Z2

Y3

Z3

DTE

0

1

0

0

1

Z

Z

DTE

0

1

1

1

0

Z

Z

DCE or All ON

1

X

0

0

1

0

1

DCE or All ON

1

X

1

1

0

1

0

Shutdown

0

0

X

Z

Z

Z

Z

Receiver

INPUTS

OUTPUTS

CONFIGURATION

S1 S2 OE

B A

R1 AND R2

R3

DTE or All ON

X

1

0

0.2V

1

1

DTE or All ON

X

1

0

0.2V

0

0

DCE

1

0

0

0.2V

1

Z

DCE

1

0

0

0.2V

0

Z

Disabled

X

X

1

X

Z

Z

Shutdown

0

0

X

X

Z

Z

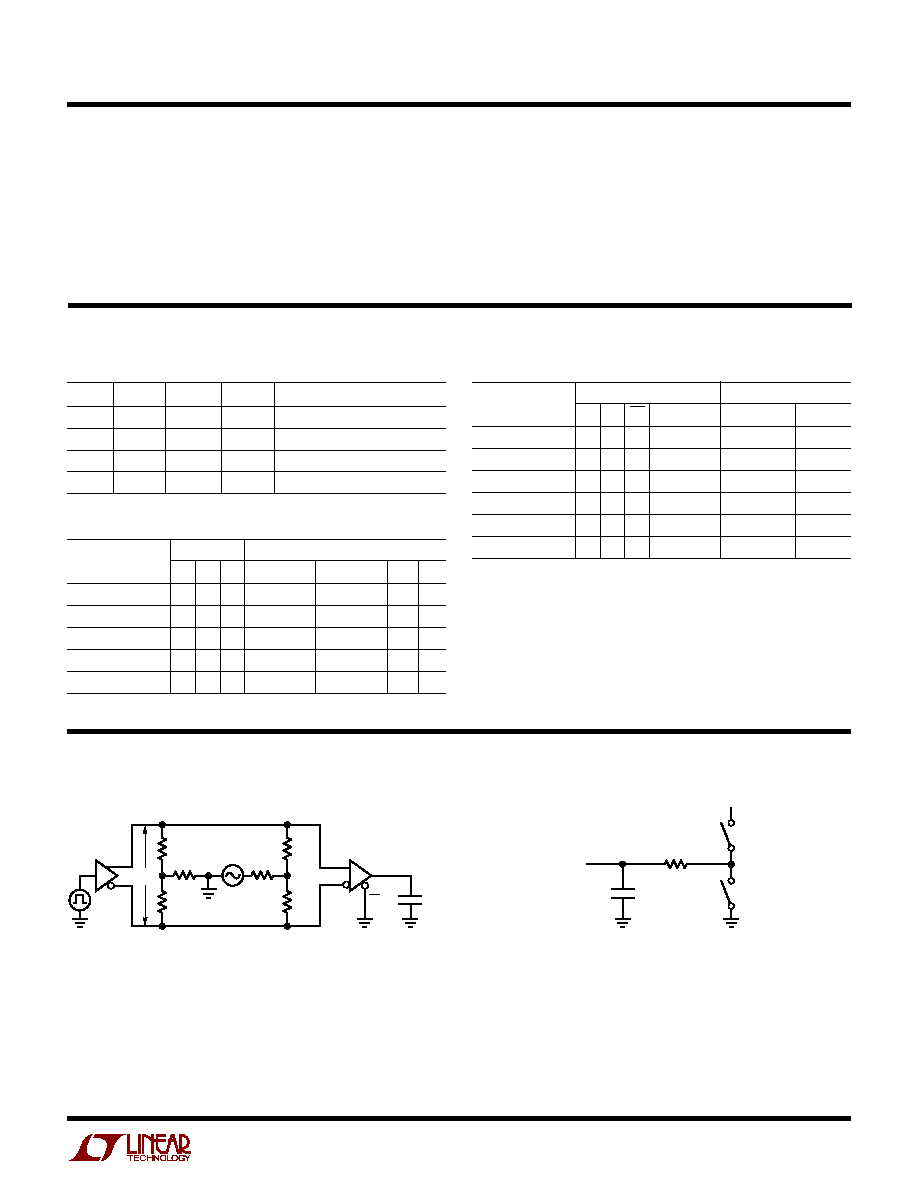

15pF

OE

R

50

125

Y

Z

Z

Y

T

125

50

50

LTC1345 · F01

50

B

A

V

OD

V

OS

V

OC

= (V

Y

+ V

Z

)/2

Figure 1. V.35 Transmitter/Receiver Test Circuit

Figure 2. Receiver Output Enable/Disable Timing Test Load

C

L

1k

LTC1345 · F02

S1

S2

V

CC

RECEIVER

OUTPUT

U

U

U

PI FU CTIO S

FU CTIO TABLES

U

U

TEST CIRCUITS